On Testing Circuit Marginalities

Duration: Full day

Target Audience: Practicing Engineers, Design Professionals, Students and Academics

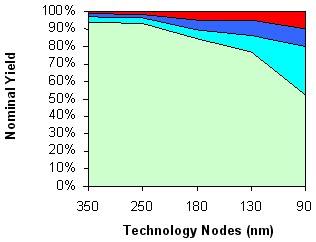

Background: Goal of testing is to screen out the manufactured parts that do not meet all functionality and performance specifications. The following are some of the typical reasons for a chip failure:

- Particulate Defects:

Random particulates embedded into manufactured part. The particulates can come from suspended particles, contamination, CMP slurry or similar sources.

- Sub-wavelength lithography:

Sub-wavelength lithography can create corner rounding, line end shortening, missing lines, shorts, missing vias etc. These problems may be exacerbated by defocus that may result from non-planarity of the surface. CMP process may not leave a surface completely planar due to density, platten position vs. platten and carrier speed issues.

- Design centering problems:

VT, Leff, ILD thickness show variance across die, wafer and lot. Some of it is related to lithography and some of it is related to process metrology used during manufacturing. Typical design process deals with them by guardbanding a design. It is generally possible to predict the areas where performance or functionality problems will show up and therefore develop targeted test content.

- Design Validation Problems:

This can subcategorized into two buckets:

-

-

- a. Design Approximations: Design process involves successive levels of approximation starting with cell characterization, interconnect extraction, model order reduction, simple delay equations, static timing analysis etc.. If scrutinized under microscope, these simplifications can all add up to an event that may cause circuit failure (examples will be provided).

-

- b. Time to Market: With an explosive number of checking tools (signal integrity, power supply integrity, reliability checks such as electromigration or NBTI vulnerability etc.) the number of design violations that are flagged is very large. Most of these violations are false negatives and are due to overly simplifying assumptions used in the checking tools themselves. Designsers often ignore the violations to be in market on time and may potentially be swallowing a poison capsule.

|